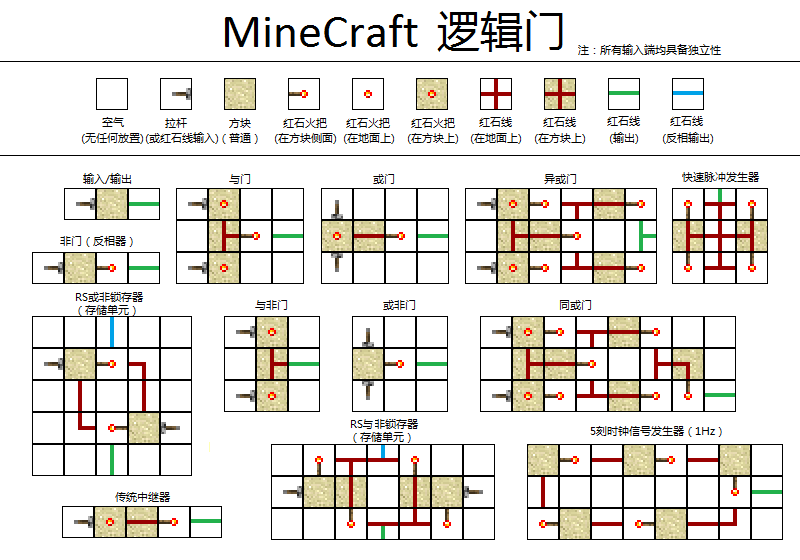

我的世界红石教程2:RS锁存器

逻辑门的特点是能够实现即时的逻辑计算——但如果仅仅是顺序组合逻辑门的话无法实现数据的存储。

这样,RS基本锁存器就是这样的一个神物——顾名思义,一个单元能够把1位二进制的数据“锁”在里面。尽管看起来简陋,但它是现在各种存储器件(内存硬盘U盘Cache等等等等)的理论基础。而且RS触发器在Minecraft中用处广泛,威力巨大。

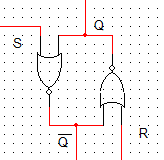

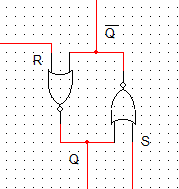

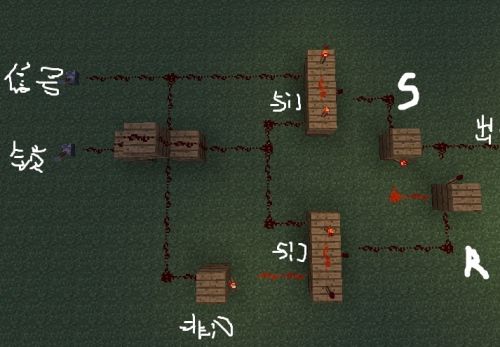

什么是RS?(有时顺序也有可能是SR)现在汉语文化圈的数字电路教材基本都是直接用RS作为中文名称而不加翻译的。R=Reset,“重置”之意,在数字电路中就是清零;S=Set,“设置”之意,在数字电路中就是置1。锁存器的设计还是采用这张图:

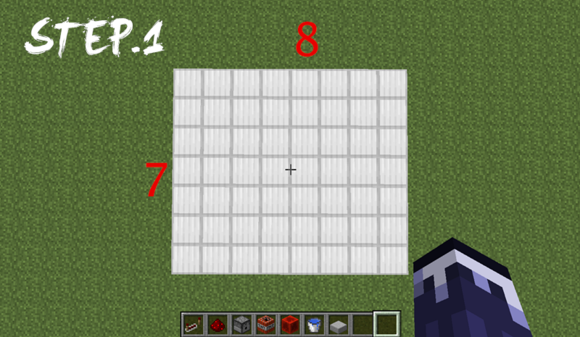

1、RS或非锁存器(RS NOR Latch)

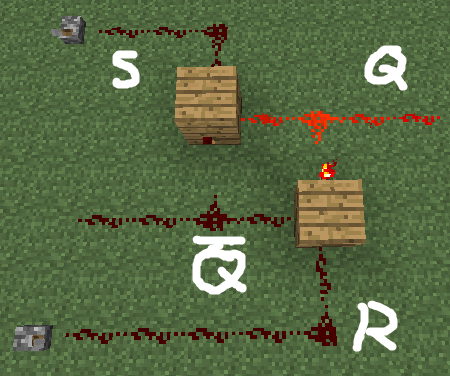

基本构造为两个或非门首尾相接。输入端为R与S;输出端为Q和“Q非”(Q上加横线那个):

足够细心的话你会发现,这不是完全中心对称的结构嘛,为什么要这么规定R与S呢?当然,互换R、S和两个输出端后,下面这样也是可以的。如何应用全看你的规定:

功能:当R与S均为低电平,锁存器状态不变(即“锁存”状态)

当R为高电平,S为低电平时,Q=0,“Q非”=1(即“清零”状态)

当S为高电平,R为低电平时,Q=1,“Q非”=0(即“置1”状态)

R与S均为高电平的情况在RS锁存器的应用中是被禁止的。原因是此时你无法预测其输出。

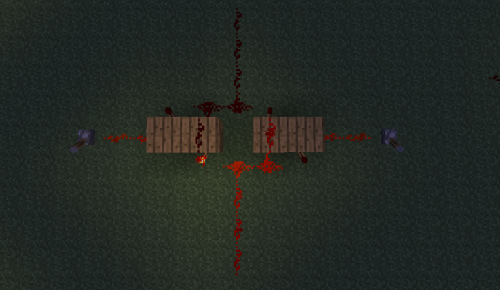

图(红色代表激活“1”,黑色代表未激活“0”):

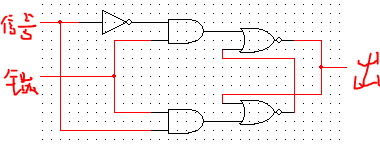

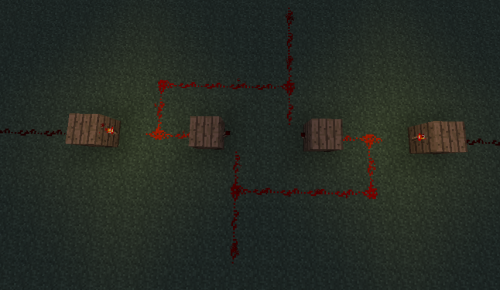

利用RS锁存器的原理我们可以实现信息存储。例如这样应用:“锁”输入端为高电平时,输出端直接与”信号“端相同;“锁”输入端为低电平时,输出保持不变,且”信号“端无论是多少都不会影响输出端,从而实现信息存储。下图的整体被称为门控型D锁存器(Gated D Latch。”D“在这里代表Data,“数据”之意),”锁存“信号高电平时有效。

2、RS与非锁存器(RS NAND Latch)

核心和RS或非锁存器一样。只不过两个输入端都加上了一个非门,从而相当于变成两个与非门首尾相接了(为什么?这我就不解释了……涉及逻辑代数计算)。命名时S与R就要变成"S非"与"R非"了——除此之外和RS或非锁存器一样。而且考虑到材料节省的原则,推荐大家采用RS或非锁存器。

等效于下面的设计。可以看到就相当于RS或非锁存器的R端S端都加一个非门。

RS单元是各种锁存器与触发器的基础(实际上“锁存器”(Latch)与“触发器”(Flip-Flop)可以混为一谈。唯一不同:“锁存器”一般是以存储为目的时的称呼,“触发器”一般是以随时间特定变化的信号为目的的称呼)。那个门控D锁存器实际上可以被表述为“高电平触发的D触发器”